公司新闻

锐石创芯重磅推出先进封装工艺射频前端接收模组

2022.12.23

锐石创芯作为业内知名的射频器件供应商,凭借雄厚的研发实力和前端设计经验,以PA为基石积极布局和扩展射频前端产品,紧跟模组化市场大趋势,坚持不断创新的理念,积极实践并推出基于先进封装工艺的分集接收模组,来满足手机、平板、IoT物联网模块等消费类产品需求,收发两端齐头并进,为客户提供全面的解决方案,也进一步加速了射频模组国产化替代进程。

随着5G的不断发展,手机终端类产品功能需求更加丰富,蜂窝从5G向下兼容4G,3G,以及2G,同时GPS,WIFI,BT,NFC样样具备,旗舰机型还会有UWB,卫星通讯等强大的通信能力,不仅如此,用户还期望更强电池续航能力,更轻便更美观的外形,这就形成了功能越来越多,却没有相应增加足够的空间给射频前端系统布局的局面。因此,为了应对极其复杂的终端设计挑战,采用高集成度的射频模组成为必然的行业趋势。

与此同时,蜂窝物联网市场有着同样的诉求,高集成度射频模组有着先天的优势,面积小,调试简单,能够帮助设计者加快产品开发速度,大幅度提升产品开发的简易性,缩短产品上市时间并降低成本,这使客户推出更小更具竞争力的产品成为可能。为支持客户研发出前瞻性产品,锐石创芯始终紧跟市场最新趋势,利用持续创新的技术及设计来满足客户需求。

针对这样的市场及用户需求,锐石创芯在分集模组上推出了一系列产品:RR85014-11,RR85013-11及RR85010-11,并将很快推出专为国内SA Only设计的DiFEM产品,来满足国内和海外现存市场和未来市场的大量需求,这一系列产品集成了单刀多掷开关(SPnT)或双刀多掷开关(DPnT)及SAW滤波器,并采用了先进的裸Die封装技术来提高集成度和降低产品成本。

1、DiFEM系列产品功能框图

2、DiFEM系列产品特性

- 覆盖国内/海外一些主要频段

Band66(1)/2/3/26(5)/7/8/34/39/40/41F

- 集成Bare Die滤波器,无需集成额外SMD器件

- 集成天线大开关

- 支持多个LB,MHB AUX端口,提供灵活的频段扩展

- 开关Multi-on功能可支持多种CA组合

- MIPI2.1通信协议

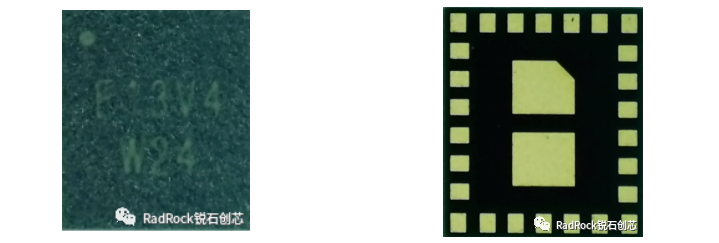

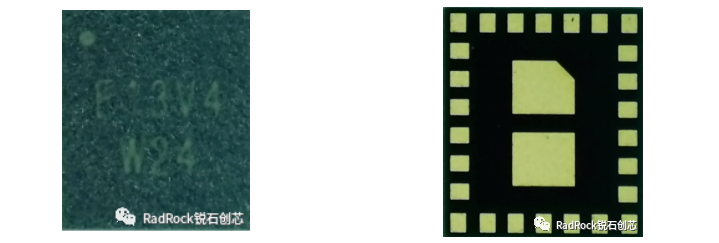

- LGA 封装

- 两种尺寸

3.2mmx3.0mmx0.7mm

3.7mmx3.2mmx0.7mm

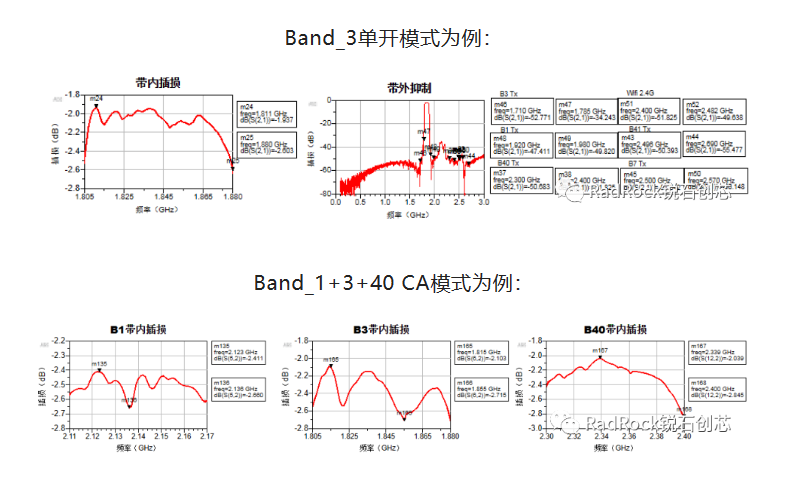

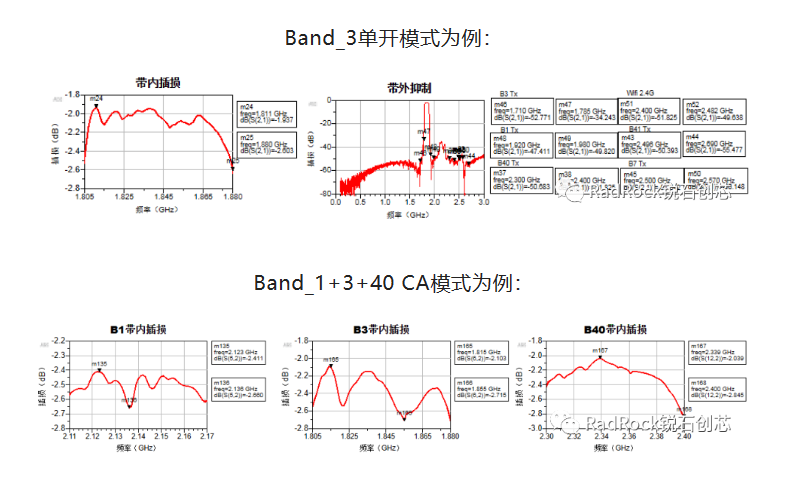

3、实测数据

实测数据实测数据显示各个频段都有非常小的带内插损及波动,同时也实现了非常好的带外抑制效果,即使在CA(Carrier Aggregation载波聚合)模式下,也保证了良好的插损和抑制特性。

4、设计能力

锐石创芯在产品开发过程中,十分注重内部器件之间的联合设计,仿真与实测相结合不断优化打磨,有效减少了内部器件之间的匹配损耗,满足了极高的工艺要求,Die上匹配也使整个设计避免了使用SMD器件,性能上表现出很强的稳定性。

锐石创芯DIFEM研发团队开发出完善的仿真流程和方法,获得了高度的仿真和测试一致性。仿真的准确性促进了产品性能设计的最优化和最大程度上缩短实验室调试的时间,进而缩短了模组的设计周期。

下图为Band_1的仿测对比示例,可以看出,在插损,带外抑制和回波方面都具有很高的对齐度。

5、先进封装工艺

锐石创芯所采用的封装有别于业内其它厂商使用的传统CSP和WLP封装,它是将滤波器、开关等裸芯片封装于模组内,免去了常见模组中单颗滤波器需要先进行CSP封装或WLP封装后再进行模组封装的过程。不仅大大减少了生产制造流程,降低了成本,还减小了模组体积,提高了模组的集成度;另一方面,在结构和流程上的简化,使得模组的制造的工艺兼容性更强,模组自身的可靠性能力更好,高温返修性能也更稳定。

具备以下优势:

高集成度:裸芯片直接封装于模组内部,减少模组尺寸

更薄的模组厚度:全FC裸芯片贴装,可拥有更低产品厚度

通用封装工艺:主要封装流程与SIP封装设备通用,便于产能扩充及调配

高可靠性:可承受不低于5次的回流生产制程,并满足相应的可靠性要求

新产品期待

随着5G的不断发展,手机终端类产品功能需求更加丰富,蜂窝从5G向下兼容4G,3G,以及2G,同时GPS,WIFI,BT,NFC样样具备,旗舰机型还会有UWB,卫星通讯等强大的通信能力,不仅如此,用户还期望更强电池续航能力,更轻便更美观的外形,这就形成了功能越来越多,却没有相应增加足够的空间给射频前端系统布局的局面。因此,为了应对极其复杂的终端设计挑战,采用高集成度的射频模组成为必然的行业趋势。

与此同时,蜂窝物联网市场有着同样的诉求,高集成度射频模组有着先天的优势,面积小,调试简单,能够帮助设计者加快产品开发速度,大幅度提升产品开发的简易性,缩短产品上市时间并降低成本,这使客户推出更小更具竞争力的产品成为可能。为支持客户研发出前瞻性产品,锐石创芯始终紧跟市场最新趋势,利用持续创新的技术及设计来满足客户需求。

针对这样的市场及用户需求,锐石创芯在分集模组上推出了一系列产品:RR85014-11,RR85013-11及RR85010-11,并将很快推出专为国内SA Only设计的DiFEM产品,来满足国内和海外现存市场和未来市场的大量需求,这一系列产品集成了单刀多掷开关(SPnT)或双刀多掷开关(DPnT)及SAW滤波器,并采用了先进的裸Die封装技术来提高集成度和降低产品成本。

1、DiFEM系列产品功能框图

2、DiFEM系列产品特性

- 覆盖国内/海外一些主要频段

Band66(1)/2/3/26(5)/7/8/34/39/40/41F

- 集成Bare Die滤波器,无需集成额外SMD器件

- 集成天线大开关

- 支持多个LB,MHB AUX端口,提供灵活的频段扩展

- 开关Multi-on功能可支持多种CA组合

- MIPI2.1通信协议

- LGA 封装

- 两种尺寸

3.2mmx3.0mmx0.7mm

3.7mmx3.2mmx0.7mm

3、实测数据

实测数据实测数据显示各个频段都有非常小的带内插损及波动,同时也实现了非常好的带外抑制效果,即使在CA(Carrier Aggregation载波聚合)模式下,也保证了良好的插损和抑制特性。

4、设计能力

锐石创芯在产品开发过程中,十分注重内部器件之间的联合设计,仿真与实测相结合不断优化打磨,有效减少了内部器件之间的匹配损耗,满足了极高的工艺要求,Die上匹配也使整个设计避免了使用SMD器件,性能上表现出很强的稳定性。

锐石创芯DIFEM研发团队开发出完善的仿真流程和方法,获得了高度的仿真和测试一致性。仿真的准确性促进了产品性能设计的最优化和最大程度上缩短实验室调试的时间,进而缩短了模组的设计周期。

下图为Band_1的仿测对比示例,可以看出,在插损,带外抑制和回波方面都具有很高的对齐度。

5、先进封装工艺

锐石创芯所采用的封装有别于业内其它厂商使用的传统CSP和WLP封装,它是将滤波器、开关等裸芯片封装于模组内,免去了常见模组中单颗滤波器需要先进行CSP封装或WLP封装后再进行模组封装的过程。不仅大大减少了生产制造流程,降低了成本,还减小了模组体积,提高了模组的集成度;另一方面,在结构和流程上的简化,使得模组的制造的工艺兼容性更强,模组自身的可靠性能力更好,高温返修性能也更稳定。

具备以下优势:

高集成度:裸芯片直接封装于模组内部,减少模组尺寸

更薄的模组厚度:全FC裸芯片贴装,可拥有更低产品厚度

通用封装工艺:主要封装流程与SIP封装设备通用,便于产能扩充及调配

高可靠性:可承受不低于5次的回流生产制程,并满足相应的可靠性要求

新产品期待

锐石创芯2023年还将推出更新一代适用于国内SA Only的双天线小尺寸DiFEM RR8501x-11,并将集成B28F滤波器,进一步简化了客户当前需要外置B28F滤波器的设计,将在成本和空间上都为客户带来明显收益。

相关新闻